## GigaComm<sup>™</sup> (SiGe) SPICE Modeling Kit

The objective of this kit is to provide sufficient circuit schematic and SPICE parameter information to perform system level interconnect modeling for devices in ON Semiconductor's high performance GigaComm (Silicon Germanium) logic family. The family have output edge rates as low as 20 ps and power supply levels of as low as 2.5 V. The kit is not intended to provide information necessary to perform circuit level modeling on the

The kit contains representatives of input and output schematics, netlists, and waveform used for the GigaComm family devices. This application note will be modified as new devices are added. Table 1 describes the nomenclature used for modeling the schematic and netlist

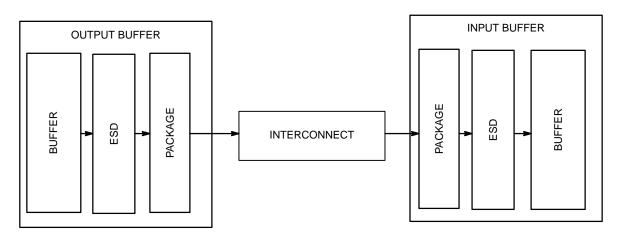

for GigaComm devices. The subcircuit models, such as

input or output buffers, ESD and package simulate only device input or output paths. When used with interconnect models, a complete signal path may be modeled as shown

Prepared by:

Objective

in Figure 1.

Senad Lomigora and Paul Shockman

GigaComm (SiGe) devices.

Schematic Information

## ON Semiconductor®

http://onsemi.com

## **APPLICATION NOTE**

#### **Table 1. Schematics and Netlist Nomenclature**

| Parameter            | Function Description                                                           |

|----------------------|--------------------------------------------------------------------------------|

| V <sub>CC</sub>      | 2.5/3.3 V for LVPECL and 0 V for LVECL                                         |

| V <sub>EE</sub>      | -2.5/-3.3 V for LVPECL and 0 V for LVECL                                       |

| $V_{BB}$ or $V_{MM}$ | Output Voltage Reference<br>(See Device Data Sheet)                            |

| V <sub>CS</sub>      | Internally Generated Voltage ( $\approx$ V <sub>EE</sub> + 1.1 V $\pm$ 50 mV)* |

| GND                  | Ground 0 V                                                                     |

| IN                   | True Input to CKT                                                              |

| INB                  | Inverted Input to CKT                                                          |

| Q                    | True Output of CKT                                                             |

| QB                   | Inverted Output of CKT                                                         |

\*Note that the NBSG16VS, NBSG53A, NBSG72A, and NBSG86A are using  $V_{CS}$  to modulate the output amplitude (see device specifics for more details).

#### Figure 1. Interconnect Model Template

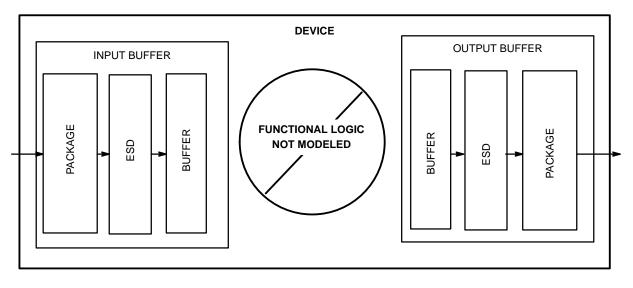

For device modeling, the behavioral LOGIC or gate functionality is not modeled (see Figure 2. DEVICE Model Template)

Figure 2. DEVICE Model Template

#### Package

A worst-case model for various package types is included to improve the accuracy of the system model (see Table 2). The package model represents the parasitics as they are measured a sizable distance from an AC ground pin. The package models should be placed on all external inputs to an input model, all external outputs for an output model and the  $V_{CC}$  line. Since the current in the  $V_{EE}$  pin is a constant, a package model for  $V_{EE}$  pin is not necessary. Please note that an internal  $V_{CS}$  voltage does not require a package model.

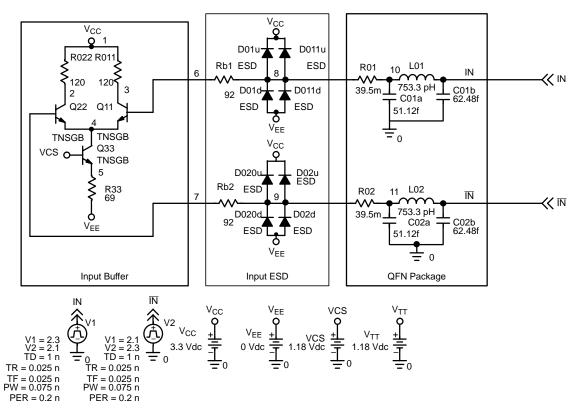

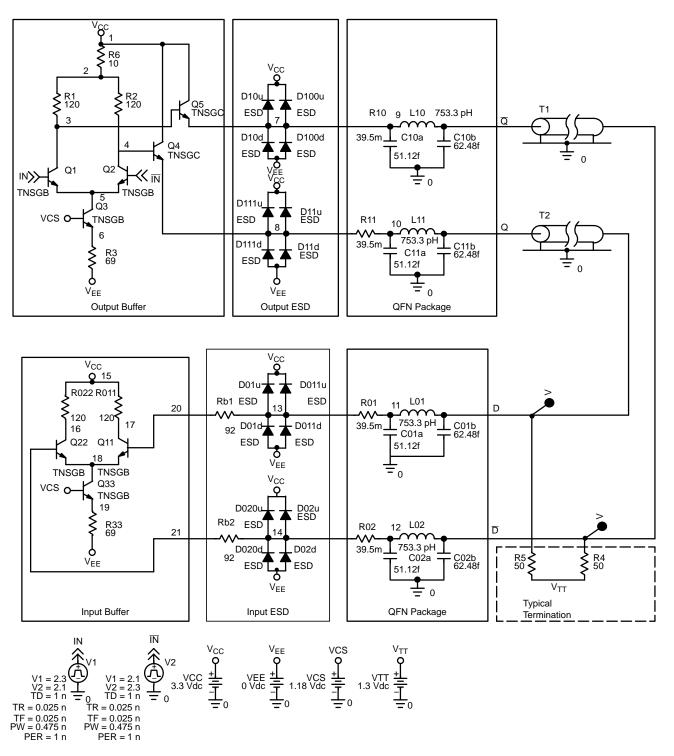

To shorten and speed up the simulation process, the simplified QFN or BGA package model should be used. The input and output buffers schematic include the simplified QFN package model (Figures 4, 5, and 8).

| Package Model | Page Number |

|---------------|-------------|

| 16–FCBGA      | 13          |

| 16–QFN        | 17          |

#### **Input Buffer**

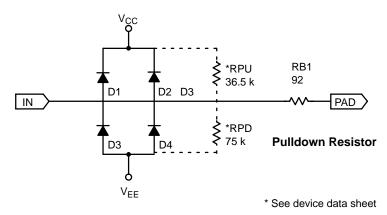

The "SG\_INBUF" schematic and netlist are representing the input structures of devices for GigaComm family devices. The schematics require the addition of ESD and package models to be accurate; but are otherwise functionally correct. It is unnecessary to include an ESD or Package model for the V<sub>BB</sub> or V<sub>MM</sub> type pins of the models because V<sub>BB</sub> type input is intended as an internal node for most applications. If a V<sub>BB</sub> type input is modeled as an external node it is usually bypassed because it is a constant voltage, and adding ESD and Package parameters provide no additional benefit.

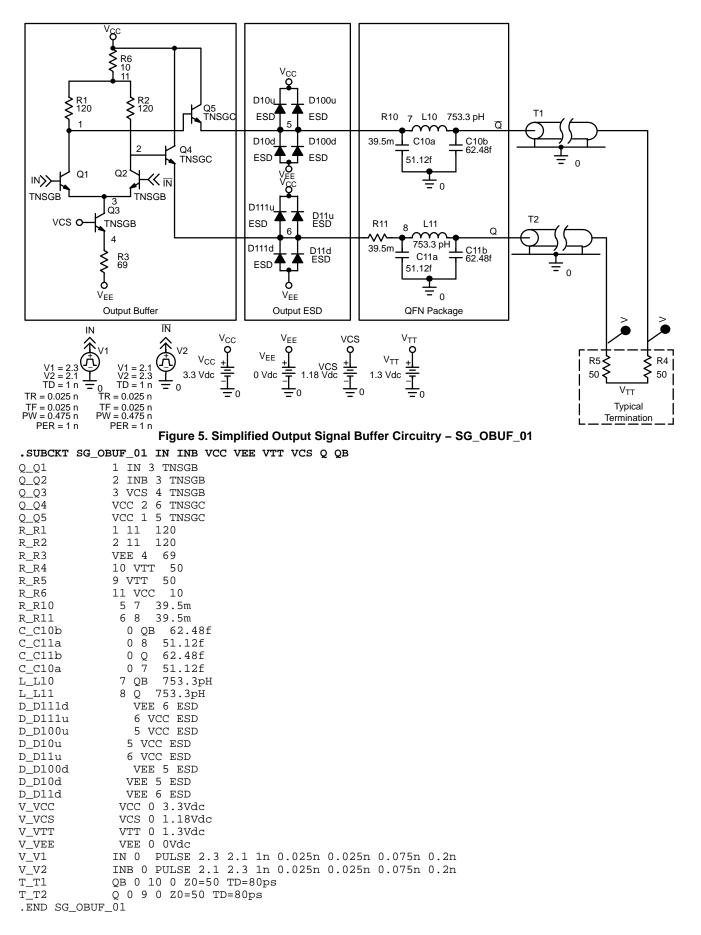

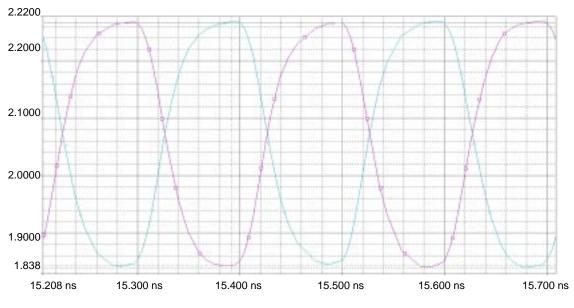

#### **Output Buffer**

Two output buffer schematics and netlists are modeled and can be seen on pages 6 and 8. The package models with all parasitics should be added for better accuracy. Any input or output that is driving or being driven by an off chip signal should include the ESD and package models. Open or floating pins will not require any ESD or package models. The output buffer models typically show internal differential inputs and outputs and should always be simulated with both output lines terminated, even when only one line or single ended use is intended. This will balance the output buffer's load.

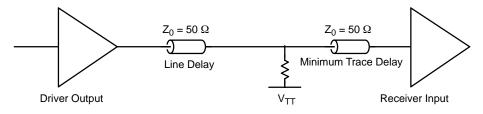

#### **Example of the Typical Interconnect Circuit**

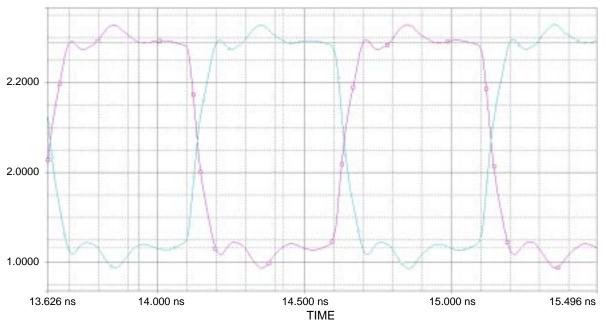

The output signal buffer SG\_0BUF\_01 with the ESD protection structure and the simplified package model properly terminated, driving the simplified input structure is shown in the Figure 13. The circuit provides working schematics of complete interconnect modeling. The output waveform observed at the receiver of the interconnect example is shown in the Figure 14.

### SPICE Netlist

The netlists are organized as a group of subcircuits. In each subcircuit model netlist, the model name should be followed by a list of external node interconnects. When copying "SUBCKT" netlist files to your text editor, use Adobe® Acrobat® Reader® 4.0 or higher to ensure proper conversion.

### **SPICE Parameter Information**

In addition to the schematics and netlists there is a listing of the SPICE parameters for the transistors referenced in the schematics and netlists. These parameters represent a typical device of a given transistor. Varying the typical parameters will affect the DC and AC performance of the structures; but for the type of modeling intended by this note, the actual delay times are not necessary and are not modeled, as a result variation of the device parameters are meaningless. The performance levels are more easily varied by other methods and will be discussed in the next section. The resistors referenced in the schematics are polysilicon and have no parasitic capacitance in the real circuit and none is required in the model. The schematics display only the devices needed in the SPICE netlists.

#### **Modeling Information**

The bias drivers for the devices are not included as they are unnecessary for interconnect simulations and their use results in a large increase in model complexity and simulation time. The internal reference voltages ( $V_{BB}$ ,  $V_{CS}$ , etc.) should be driven with ideal constant voltage sources. If a GigaComm device is used in positive mode the levels vary one to one with the power supply; but are constant as a function of temperature.

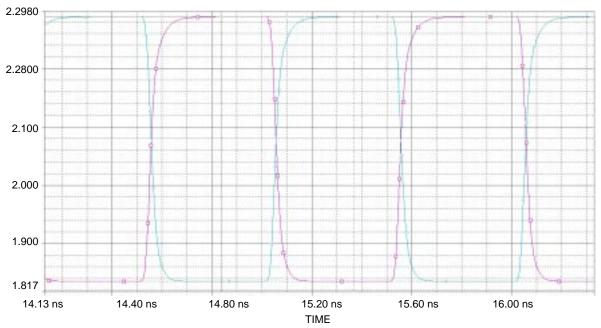

The schematics and SPICE parameters will provide a typical output waveform, which can be seen in Figures 9 and 10. Note that ESD and package models will add 5 ps–7 ps to rise and fall time of the output waveform. Simple adjustments can be made to the models allowing output characteristics to simulate conditions at or near the corners of the data book specifications. Consistent cross–point voltages need to be maintained.

#### • To adjust rise and fall times:

Produce the desired rise and fall times output slew rates by adjusting collector load resistors to change the gates tail current. The  $V_{CS}$  voltage will affect the tail current in the output differential, which will interact with the load resistor and collector resistor to determine  $t_r$  and  $t_f$ at the output.

#### • To adjust the V<sub>OH</sub>:

Adjust the  $V_{OH}$  and  $V_{OL}$  level by the same amount by varying  $V_{CC}$ . The output levels will follow changes in  $V_{CC}$  at a 1:1 ratio.

#### • To adjust the V<sub>OL</sub> only:

Adjust the V<sub>OL</sub> level independently of the V<sub>OH</sub> level by increasing or decreasing the collector load resistance. Note that the V<sub>OH</sub> level will also change slightly due to an I<sub>BASE</sub> R drop across the collector load resistor. The V<sub>OL</sub> can be changed by varying the V<sub>CS</sub> supply, and therefore the gate current through the current source resistor.

#### Device Specifics NBSG16VS

The NBSG16VS is a differential receiver/driver with variable output amplitude which is controlled by a voltage applied to  $V_{CRTL}$  over the range of  $V_{CC}$  to  $V_{CC} - 2 V$ . These  $V_{CTRL}$  voltages produce corresponding output amplitudes over the range of 75 mV to 750 mV (see Data Sheet Figure 11). The SPICE model for NBSG16VS simulates seven selected swings within the output amplitude range by adjusting  $V_{CS}$  to one of seven voltages per Table 3. Simulation tr/tf represents the worst case (fastest) edges. A DC offset must be applied to all voltages to convert LVNECL to LVPECL at a 1:1 ratio.

#### NBSG53A, NBSG72A, and NBSG86A

The NBSG53A, NBSG72A, and NBSG86A are multifunctional differential GigaComm devices with Output Level Select (OLS) capability. The OLS input pin is used to program the peak–to–peak output amplitude between 0 mV and 800 mV in five discrete steps. When simulating output of the NBSG53A, NBSG72A, or NBSG86A, use Table 3,  $V_{CS}$  value from line 3, 5, 7, or 10 to obtain desired output amplitude swing.

# Table 3. Required $V_{CS}$ for Selected Output Amplitudes of the NBSG16VS

| Output Amplitude (mV) |     | V <sub>CS</sub> (V)     |

|-----------------------|-----|-------------------------|

| 1.                    | 75  | V <sub>EE</sub> + 0.865 |

| 2.                    | 100 | V <sub>EE</sub> + 0.9   |

| 3.                    | 200 | V <sub>EE</sub> + 0.98  |

| 4.                    | 300 | V <sub>EE</sub> + 1.06  |

| 5.                    | 400 | V <sub>EE</sub> + 1.15  |

| 6.                    | 500 | V <sub>EE</sub> + 1.23  |

| 7.                    | 600 | V <sub>EE</sub> + 1.3   |

| 8.                    | 700 | V <sub>EE</sub> + 1.38  |

| 9.                    | 750 | V <sub>EE</sub> + 1.42  |

| 10.                   | 800 | V <sub>EE</sub> + 1.46  |

### Summary

The information included in this kit provides adequate information to run a SPICE level system interconnect simulation. The block diagram in Figure 3 illustrates a typical situation, which can be modeled using the information in this kit. Device input or output models are presented in Table 4.

Figure 3. Typical Application for I/O SPICE Modeling Kit

#### Table 4. GigaComm Input/Output Buffer Selector Guide

| Device   | Function                                                                                      | Input Model | Output Model |

|----------|-----------------------------------------------------------------------------------------------|-------------|--------------|

| NB7L11M  | 2.5/3.3 V 1:2 Differential Clock/Data Driver with CML Outputs                                 | SG_INBUF    | SG_OBUF_02   |

| NB7L14M  | 2.5/3.3 V 1:4 Differential Clock/Data Driver with CML Outputs                                 | SG_INBUF    | SG_OBUF_02   |

| NB7L86M  | 2.5/3.3 V Differential Smart Gate with CML Outputs                                            | SG_INBUF    | SG_OBUF_02   |

| NBSG11   | 2.5/3.3 V Differential Clock Driver with RSECL Outputs                                        | SG_INBUF    | SG_OBUF_01   |

| NBSG14   | 2.5/3.3 V Differential Receiver/Driver with RSECL Outputs                                     | SG_INBUF    | SG_OBUF_01   |

| NBSG16   | 2.5/3.3 V Differential Receiver/Driver with RSECL Outputs                                     | SG_INBUF    | SG_OBUF_01   |

| NBSG16VS | 2.5/3.3 V Differential Receiver/Driver with Variable Output Swing                             | SG_INBUF    | SG_OBUF_01*  |

| NBSG16M  | 2.5/3.3 V Differential CML Receiver/Driver                                                    | SG_INBUF    | SG_0BUF_02   |

| NBSG53A  | 2.5/3.3 V Selectable Differential Clock and Data D Flip-Flop/Clock Divider with Reset and OLS | SG_INBUF    | SG_OBUF_01*  |

| NBSG72A  | 3.5/3.3 V Differential CML 2x2 Crosspoint Switch with OLS                                     | SG_INBUF    | SG_OBUF_01*  |

| NBSG86A  | 2.5/3.3 V Differential Smart Gate with OLS                                                    | SG_INBUF    | SG_OBUF_01*  |

\*Note: See Device Specifics and Table 3 for Details.

| Figure 4. Simplified Input Circ | uitry – SG_INBUF |

|---------------------------------|------------------|

|---------------------------------|------------------|

| .SUBCKT SG_I | NBUF IN INB VCC VEE VCS                          |

|--------------|--------------------------------------------------|

| Q_Q11        | 3 6 4 TNSGB                                      |

| Q_Q22        | 2 7 4 TNSGB                                      |

| Q_Q33        | 4 VCS 5 TNSGB                                    |

| R_R011       | 3 VCC 120                                        |

| R_R022       | 2 VCC 120                                        |

| R_R33        | VEE 5 69                                         |

| R_Rb1        | 6 8 92                                           |

| R_Rb2        | 9 7 92                                           |

| R_R01        | 8 10 39.5m                                       |

| R_R02        | 9 11 39.5m                                       |

| L_L01        | 10 IN 753.3pH                                    |

| L_L02        | 11 INB 753.3pH                                   |

| D_D01d       | VEE 8 ESD                                        |

| D_D011d      | VEE 8 ESD                                        |

| D_D02d       | VEE 9 ESD                                        |

| D_D020d      | VEE 9 ESD                                        |

| D_D01u       | 8 VCC ESD                                        |

| D_D011u      | 8 VCC ESD                                        |

| D_D02u       | 9 VCC ESD                                        |

| D_D020u      | 9 VCC ESD                                        |

| C_C01a       | 0 10 51.12f                                      |

| C_C02a       | 0 11 51.12f                                      |

| C_C01b       | 0 IN 62.48f                                      |

| C_C02b       | 0 INB 62.48f                                     |

| V_VCC        | VCC 0 3.3Vdc                                     |

| V_VCS        | VCS 0 1.18Vdc                                    |

| V_VEE        | VEE 0 0Vdc                                       |

| V_V1         | IN 0 PULSE 2.3 2.1 1n 0.025n 0.025n 0.075n 0.2n  |

| V_V2         | INB 0 PULSE 2.1 2.3 1n 0.025n 0.025n 0.075n 0.2n |

| .END SG_INBU | IF                                               |

Figure 6. Typical Output Waveform of the SG\_OBUF\_01 at 1 GHz (tr = 34 ps, tf = 32 ps, Voutpp = 451 mV, Voh = 2.288 V, Vol=1.835 V)

TIME

Figure 7. Typical Output Waveform of the SG\_OBUF\_01 at 5 GHz (tr = 32 ps, tf = 30 ps, Voutpp = 422 mV, Voh = 2.26 V, Vol = 1.84 V)

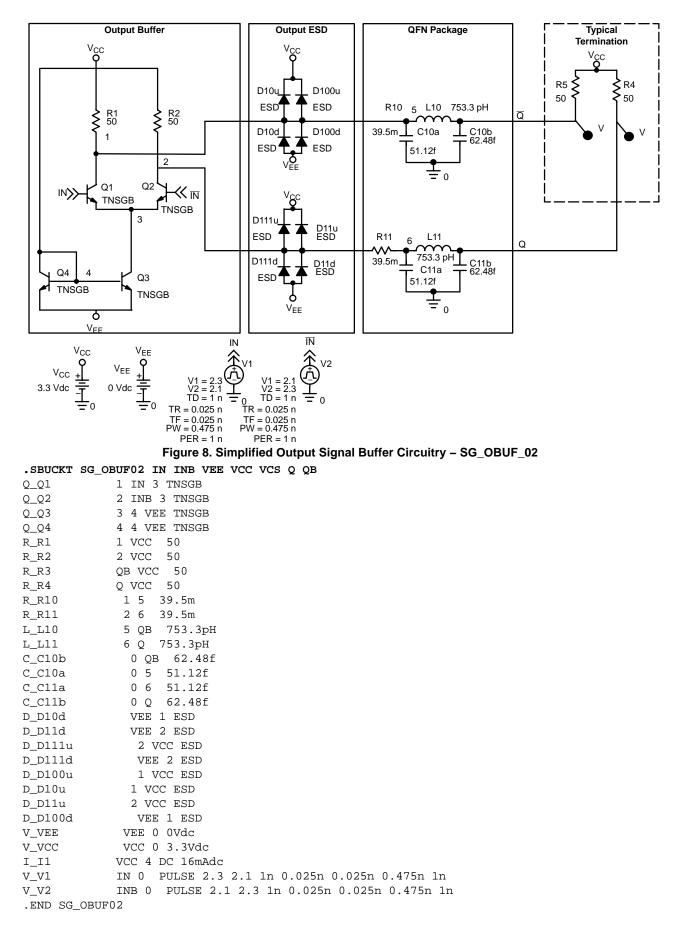

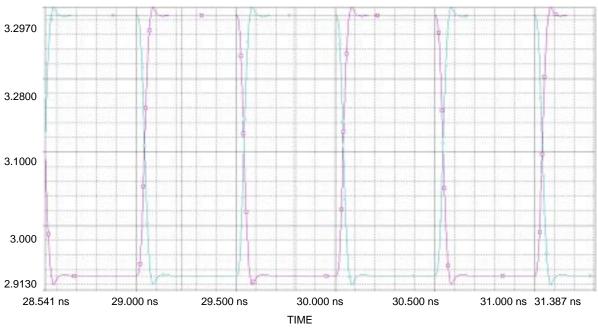

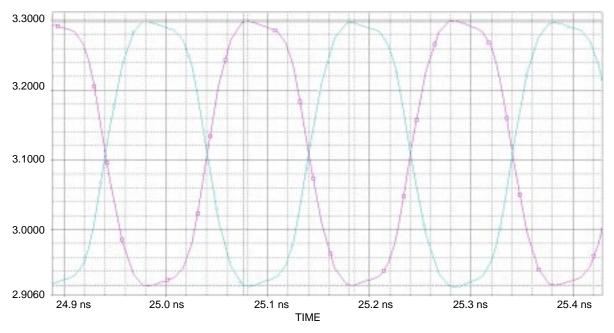

Figure 9. Typical Output Waveform of the SG\_OBUF\_02 at 1 GHz (tr = 30 ps, tf = 28 ps, Voutpp = 354 mV, Voh = 3.29 V, Vol = 2.93 V)

Figure 10. Typical Output Waveform of the SG\_OBUF\_02 at 5 GHz (tr = 29 ps, tf = 28 ps, Voutpp = 364 mV, Voh = 3.29 V, Vol = 2.92 V)

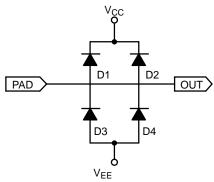

| .SUBCKI | IN_ESD | VCC VEE | IN PAD |

|---------|--------|---------|--------|

| D1      | IN     | VCC     | ESD    |

| D2      | IN     | VCC     | ESD    |

| D3      | VEE    | IN      | ESD    |

| D4      | VEE    | IN      | ESD    |

|         |        |         |        |

| RPD     | IN     | VEE     | 75K    |

| RPU     | IN     | VCC     | 36.5K  |

| RB1     | IN     | PAD     | 92     |

| .ENDS I | N_ESD  |         |        |

Figure 12. Output ESD

| .SUBCKT  | OUT_   | ESD | VCC | VEE | OUT |

|----------|--------|-----|-----|-----|-----|

| D1       | OUT    |     | VC  | C   | ESD |

| D2       | OUT    |     | VC  | C   | ESD |

| D3       | VEE    |     | OUT |     | ESD |

| D4       | VEE    |     | OUT |     | ESD |

| .ENDS OU | JT_ESI | D   |     |     |     |

.MODEL TNSGC NPN (IS=1.47e-16 BF=180 NF=1 VAF=96.3 IKF=1.62e-01 ISE=2.96e-15 NE=2.5 BR=20.2 VAR=2.76 IKR=1.34e-02 ISC=2.14e-16 NC=1.426 RB=25 IRB=1.50e-03 RBM=4 RE=1 RC=7 CJE=3.34e-15 VJE=.8867 MJE=.2868 TF=2.00e-12 ITF=0.25e-01 XTF=0.7 VTF=0.35 PTF=20 TR=0.5e-9 CJC=1.08e-15 VJC=0.632 MJC=0.301 XCJC=.3 CJS=8.12e-16 VJS=.4193 MJS=0.256 EG=1.119 XTI=3.999 XTB=0.8826 FC=0.9)

.MODEL TNSGB NPN (IS=2.18e-17 BF=179 NF=1 VAF=96.5 IKF=2.42e-02 ISE=3.83e-16 NE=2.5 BR=20.4 VAR=2.76 IKR=1.98e-03 ISC=2.91e-17 NC=1.426 RB=55 IRB=1.12e-04 RBM=48 RE=6 RC=11 CJE=4.98e-16 VJE=.8867 MJE=.2868 TF=2.00e-12 ITF=0.4e-02 XTF=0.7 VTF=0.6 PTF=20 TR=0.5e-9 CJC=1.55e-16 VJC=0.632 MJC=0.301 XCJC=0.3 CJS=1.71e-16 VJS=.4193 MJS=0.256 EG=1.119 XTI=3.999 XTB=0.8826 FC=0.9)

.MODEL ESD D (IS=9.99E-21 CJO=65.2E-15 RS=50.1 VJ=0.82 M=0.25 BV= 35)

Figure 13. Example of the Typical Interconnect Circuit

Figure 14. Output Waveform of the Interconnect Example Shown in Figure 13 (Frequency = 1 GHz, tr = 49 ps, tf = 53 ps, Voutpp = 455 mV)

```

_____

Package Models

* Package: 16 pin PBGA

* Model for 16 pins

* Note:

* 1. The model assume ground plane is 15 mil below package

* 2. The resistance model was calculated at 10 GHz

* PBGA drawing:

* Case Outline

:

* Conductor number-pin designation cross reference:

*

*

Conductor

Pin

*

1

Α1

*

2

Α2

*

3

A3

*

4

Α4

*

5

В1

*

6

В2

*

7

В3

*

8

в4

*

9

C1

*

10

C2

*

11

C3

*

12

C4

*

13

D1

*

14

D2

*

15

D3

*

16

D4

* number of lumps: 1

* COMPRESSION OF SUBCIRCUITS PERFORMED: discard ratio is 0.050

.SUBCKT PACKAGE NO1I NO10 NO2I NO20 NO3I NO30 NO4I NO40

+ N051 N050 N061 N060 N071 N070 N081 N080 N091 N090

+ N10I N100 N11I N110 N12I N120 N13I N130 N14I N140

+ N15I N150 N16I N160 BD_GND

N01I N01C

R01

1.640e-01

C01

N01C

BD_GND 6.333e-14

N010

8.325e-10

L01

N01C

N02C

R02

N02I

8.500e-02

BD_GND

C02

N02C

6.275e-14

N020

L02

N02C

4.373e-10

NOJI

N03C

R03

8.500e-02

N03C

C03

BD_GND 6.016e-14

L03

N03C N03O

4.361e-10

R04

N04I N04C

1.640e-01

C04

N04C BD_GND 6.660e-14

L04

N04C N04O

8.264e-10

R05

N05I N05C

8.600e-02

N05C BD_GND 5.632e-14

C05

L05

N05C N05O

4.274e-10

R06

N06I N06C

8.600e-02

BD_GND

5.457e-14

C06

N06C

N06C N06O

3.049e-10

L06

N07C

8.600e-02

R07

N07I

BD_GND

5.036e-14

C07

N07C

L07

N07C

N070

3.049e-10

```

| R08   | NO8I | N08C   | 8.600e-02 |

|-------|------|--------|-----------|

| C08   | N08C | BD GND | 6.380e-14 |

|       |      | _      |           |

| L08   | N08C | N080   | 4.280e-10 |

| R09   | N09I | N09C   | 8.600e-02 |

| C09   | N09C | BD GND | 6.423e-14 |

|       |      | _      |           |

| L09   | N09C | N090   | 4.283e-10 |

| R10   | N10I | N10C   | 8.600e-02 |

| C10   | N10C | BD GND | 5.121e-14 |

|       |      | _      |           |

| L10   | N10C | N100   | 3.052e-10 |

| R11   | N11I | N11C   | 8.600e-02 |

| C11   | N11C | BD GND | 4.875e-14 |

| L11   | N11C | N110   | 3.048e-10 |

|       |      |        |           |

| R12   | N12I | N12C   | 8.600e-02 |

| C12   | N12C | BD_GND | 6.326e-14 |

| L12   | N12C | N120   | 4.274e-10 |

|       |      |        |           |

| R13   | N13I | N13C   | 1.640e-01 |

| C13   | N13C | BD_GND | 6.028e-14 |

| L13   | N13C | N130   | 8.314e-10 |

|       |      |        |           |

| R14   | N14I | N14C   | 8.500e-02 |

| C14   | N14C | BD_GND | 5.872e-14 |

| L14   | N14C | N140   | 4.373e-10 |

|       | -    | -      |           |

| R15   | N15I | N15C   | 8.500e-02 |

| C15   | N15C | BD_GND | 6.334e-14 |

| L15   | N15C | N150   | 4.362e-10 |

|       |      |        | 1.640e-01 |

| R16   | N16I | N16C   |           |

| C16   | N16C | BD_GND | 6.609e-14 |

| L16   | N16C | N160   | 8.292e-10 |

|       | L01  | L02    | 0.2743    |

| K0102 |      |        |           |

| C0102 | N01C | N02C   | 6.160e-14 |

| K0103 | L01  | L03    | 0.0734    |

| K0105 | L01  | L05    | 0.2311    |

|       |      |        |           |

| C0105 | N01C | N05C   | 2.312e-14 |

| K0106 | L01  | L06    | 0.1381    |

| C0106 | N01C | N06C   | 8.262e-14 |

|       |      |        |           |

| K0107 | L01  | L07    | 0.0626    |

| K0109 | L01  | L09    | 0.0894    |

| K0116 | L01  | L16    | -0.0521   |

|       |      |        |           |

| K0203 | L02  | L03    | 0.2951    |

| C0203 | N02C | N03C   | 6.784e-14 |

| K0204 | L02  | L04    | 0.0682    |

| K0205 | L02  | L05    | 0.1439    |

|       |      |        |           |

| K0206 | L02  | L06    | 0.1457    |

| C0206 | N02C | N06C   | 3.281e-14 |

| K0207 | L02  | L07    | 0.1096    |

|       |      |        |           |

| K0304 | L03  | L04    | 0.2694    |

| C0304 | N03C | N04C   | 5.694e-14 |

| K0305 | L03  | L05    | 0.0515    |

| K0306 | L03  | L06    | 0.1089    |

|       |      |        |           |

| K0307 | L03  | L07    | 0.1457    |

| C0307 | N03C | N07C   | 3.349e-14 |

| K0308 | L03  | L08    | 0.1395    |

|       |      |        |           |

| K0406 | L04  | L06    | 0.0608    |

| K0407 | L04  | L07    | 0.1369    |

| C0407 | N04C | N07C   | 8.300e-14 |

|       |      |        |           |

| K0408 | L04  | L08    | 0.2289    |

| C0408 | N04C | N08C   | 2.259e-14 |

| K0412 | L04  | L12    | 0.0932    |

| K0413 | L04  | L13    | -0.0518   |

|       |      |        |           |

| K0506 | L05  | L06    | 0.1906    |

| C0506 | N05C | N06C   | 8.897e-14 |

| K0507 | L05  | L07    | 0.0682    |

|       |      |        |           |

| K0509 | L05  | L09    | 0.2806    |

|       |      |        |           |

| <b>20500</b>   | 22050       | 12000       | 6 200 14            |

|----------------|-------------|-------------|---------------------|

| C0509          | N05C        | N09C        | 6.387e-14           |

| K0510          | L05         | L10         | 0.0534              |

| К0513          | L05         | L13         | 0.0893              |

| K0607          | L06         | L07         | 0.0808              |

| K0608          | L06         | L08         | 0.0674              |

| K0609          | L06         | L09         | 0.0536              |

| K0610          | L06         | L10         | 0.0713              |

| K0611          | L06         | L11         | 0.0503              |

| K0708          | L07         | L08         | 0.1896              |

| C0708          | N07C        | N08C        | 8.678e-14           |

| K0710          | L07         | L10         | 0.0502              |

| K0711          | L07         | L11         | 0.0718              |

| K0712          | L07         | L12         | 0.0546              |

| K0811          | L08         | L11         | 0.0549              |

| K0812          | L08         | L12         | 0.2847              |

| C0812          | N08C        | N12C        | 6.539e-14           |

| K0816          | L08         | L16         | 0.0933              |

| к0910          | L09         | L10         | 0.1903              |

| C0910          | N09C        | N10C        | 8.903e-14           |

| К0911          | L09         | L11         | 0.0679              |

| к0913          | L09         | L13         | 0.2309              |

| C0913          | N09C        | N13C        | 2.387e-14           |

| к0914          | L09         | L14         | 0.1436              |

| к0915          | L09         | L15         | 0.0510              |

| K1011          | L10         | L11         | 0.0806              |

| K1012          | L10         | L12         | 0.0675              |

| K1013          | L10         | L13         | 0.1376              |

| C1013          | N10C        | N13C        | 8.341e-14           |

| K1014          | L10         | L14         | 0.1456              |

| C1014          | N10C        | N14C        | 3.117e-14           |

| K1015          | L10         | L15         | 0.1090              |

| K1016          | L10         | L16         | 0.0609              |

| K1112          | L11         | L12         | 0.1894              |

| C1112          | N11C        | N12C        | 8.742e-14           |

| K1113          | L11         | L13         | 0.0620              |

| K1114          | L11         | L14         | 0.1089              |

| к1115          | L11         | L15         | 0.1452              |

| C1115          | N11C        | N15C        | 3.130e-14           |

| K1116          | L11         | L16         | 0.1362              |

| C1116          | N11C        | N16C        | 8.281e-14           |

| K1215          | L12         | L15         | 0.1398              |

| K1215          | L12         | L16         | 0.2292              |

| C1216          | N12C        | N16C        | 2.266e-14           |

| K1314          | L13         | L14         | 0.2736              |

| C1314          | N13C        | N14C        | 5.822e-14           |

| K1315          | L13         | L15         | 0.0724              |

|                |             |             | 0.2948              |

| K1415<br>C1415 | L14<br>N14C | L15<br>N15C | 0.2948<br>6.859e-14 |

| K1415          |             | N15C<br>L16 | 0.0681              |

|                | L14<br>115  |             |                     |

| K1516          | L15         | L16<br>N16C | 0.2704              |

| C1516          | N15C        | N16C        | 6.064e-14           |

| .ENDS          | PACKAGE     |             |                     |

```

_____

_____

* Package: 16 pin QFN

* Model for 16 pins

* Note:

* 1. The model assume ground plane is 15 mil below package

* 2. The model assume flag is grounded

\star 3. The model is based on GigaComm device 1.475mm x 1.475mm

* 4. Wire bond parasitics are lumped with lead frame post.

* 5. Lump element equivalent model valid up to 10 Ghz

* Lead Frame drawing: ASAT 3mm x 3mm QFN

* Case Outline:

* LC file : 16qfn3x3.LC

* Package: GigaComm 16 pin 3mm x 3mm QFN

* Model for 16 pins

*

* Conductor number-pin designation cross reference:

*

Conductor

Pin

*

1

1

*

2

2

*

3

3

*

4

4

*

5

5

*

6

6

*

7

7

*

8

8

*

9

9

*

10

10

*

11

11

*

12

12

*

13

13

*

14

14

*

15

15

*

16

16

* number of lumps: 1

* COMPRESSION OF SUBCIRCUITS PERFORMED: discard ratio is 0.050

.SUBCKT PACKAGE NO1I NO10 NO2I NO20 NO3I NO30 NO4I NO40

+ N051 N050 N061 N060 N071 N070 N081 N080 N091 N090

+ N10I N100 N11I N110 N12I N120 N13I N130 N14I N140

+ N15I N150 N16I N160 BD_GND

R01

N01I N01C 4.300e-02

C01a

N01C BD_GND 6.674e-14

C01b N010 BD_GND 8.157e-14

T.01

N01C N010 8.418e-10

R02 N02I N02 3.950e-02

C02a N02C BD_GND 5.153e-14

C02b N020 BD_GND 6.298e-14

N02C

N020

7.557e-10

L02

R03

N03I N03C 3.950e-02

C03a

N03C BD_GND 5.364e-14

BD_GND

6.556e-14

C03b

N030

N030 7.550e-10

L03

N03C

N04C 4.300e-02

R04

N04I

C04a

N04C

BD_GND 6.687e-14

C04b

N040

BD_GND

8.173e-14

```

| 7.0.4  | 1040         | 170.40       | 0 405 10  |

|--------|--------------|--------------|-----------|

| L04    | N04C         |              | 8.427e-10 |

| R05    | N05I         |              | 4.300e-02 |

| C05a   | N05C         | BD_GND       | 6.633e-14 |

| C05b   | N050         | BD_GND       | 8.107e-14 |

| L05    | N05C         | N050         | 8.451e-10 |

| R06    | N06I         | N06C         | 3.950e-02 |

| C06a   | N06C         | BD_GND       | 5.202e-14 |

| C06b   | N060         | BD GND       | 6.358e-14 |

| L06    | N06C         | N060         | 7.560e-10 |

| R07    | N07I         | N07C         | 3.950e-02 |

| C07a   | N07C         | BD_GND       | 5.243e-14 |

| C07b   | N070         |              | 6.408e-14 |

| L07    | N07C         | N070         | 7.551e-10 |

| R08    | N07C         | N070<br>N08C | 4.300e-02 |

| C08a   | N08C         | BD_GND       | 6.682e-14 |

|        |              |              |           |

| C08b   | N080         | BD_GND       |           |

| L08    | N08C         | N080         |           |

| R09    | N09I         | N09C         | 4.300e-02 |

| C09a   | N09C         | BD_GND       | 6.606e-14 |

| C09b   | N090         | BD_GND       |           |

| L09    | N09C         | N090         | 8.418e-10 |

| R10    | N10I         | N10C         | 3.950e-02 |

| C10a   | N10C         | BD_GND       | 5.112e-14 |

| C10b   | N100         | BD_GND       | 6.248e-14 |

| L10    | N10C         | N100         | 7.533e-10 |

| R11    | N11I         | N11C         | 3.950e-02 |

| Clla   | N11C         | BD_GND       | 5.166e-14 |

| C11b   | N110         |              | 6.314e-14 |

| L11    | N11C         | N110         | 7.524e-10 |

| R12    | N12I         | N12C         | 4.300e-02 |

| C12a   | N12C         | BD_GND       | 6.786e-14 |

| C12b   | N120         | BD_GND       | 8.294e-14 |

| L12D   | N120<br>N12C | N120         |           |

|        |              | N120<br>N13C |           |

| R13    | N13I         |              |           |

| C13a   | N13C         |              | 6.628e-14 |

| C13b   | N130         | BD_GND       |           |

| L13    | N13C         | N130         |           |

| R14    | 777N14I      | N14C         | 3.950e-02 |

| C14a   | N14C         | BD_GND       |           |

|        |              | BD_GND       | 6.402e-14 |

| L14    | N14C         | N140         | 7.536e-10 |

| R15    | N15I         | N15C         | 3.950e-02 |

| C15a   | N15C         | BD_GND       | 5.310e-14 |

| C15b   | N150         | BD_GND       | 6.490e-14 |

| L15    | N15C         | N150         | 7.514e-10 |

| R16    | N16I         | N16C         | 4.300e-02 |

| C16a   | N16C         | BD_GND       | 6.692e-14 |

| C16b   | N160         | BD GND       | 8.179e-14 |

| L16    | N16C         | N160         | 8.412e-10 |

| K0102  | L01          | L02          | 0.1711    |

| C0102a |              | N02C         | 1.740e-14 |

| C0102b | N010         | N020         |           |

| K0103  | L01          | L03          | 0.0676    |

|        |              | L03<br>L15   | 0.0549    |

| K0115  | L01          |              |           |

| K0116  | L01          | L16          | 0.1085    |

| C0116a | N01C         |              |           |

| C0116b | N010         |              | 5.863e-15 |

| K0203  | L02          | L03          | 0.1574    |

| C0203a | N02C         | N03C         | 1.622e-14 |

| C0203b | N020         | N030         |           |

| K0204  | L02          | L04          | 0.0690    |

| K0216  | L02          | L16          | 0.0555    |

|        |              |              |           |

| K0304         | L03          | L04  | 0.1713                 |

|---------------|--------------|------|------------------------|

| C0304a        | N03C         | N04C | 1.744e-14              |

| C0304b        | N030         |      | 2.131e-14              |

| K0305         | L03          | L05  | 0.0563                 |

| K0405         | L04          | L05  | 0.1098                 |

| C0405a        | N04C         | N05C | 4.747e-15              |

| C0405b        | N040         | N050 | 5.803e-15              |

| K0406         | L04          | L06  | 0.0560                 |

| K0506         | L05          | L06  | 0.1723                 |

| C0506a        | N05C         | N06C | 1.739e-14              |

| C0506b        | N050         | N060 | 1.739e-14<br>2.125e-14 |

| K0507         | L05          |      |                        |

| K0607         | L06          |      | 0.1578                 |

| C0607a        | N06C         | N07C | 1.633e-14              |

| C0607b        | N060         |      | 1.996e-14              |

| K0608         | L06          | L08  |                        |

| K0708         |              | L08  | 0.1708                 |

| C0708a        | N07C         |      |                        |

|               | N070         |      | 2.136e-14              |

| K0709         | L07          | L09  | 0.0551                 |

| K0809         | L08          | L09  | 0.1085                 |

|               |              |      | 4.797e-15              |

| C0809a        | N08C<br>N080 | N09C | 4.797e-15<br>5.863e-15 |

| C0809b        |              |      |                        |

| K0810         | L08          |      |                        |

| K0910         | L09          |      | 0.1711                 |

| C0910a        | N09C         | N10C | 1.734e-14              |

| C0910b        | N090         | N100 | 2.119e-14              |

| K0911         | L09          | L11  |                        |

| K1011         | L10          |      | 0.1574                 |

| C1011a        | N10C         |      | 1.613e-14              |

| C1011b        | N100         |      | 1.972e-14              |

| K1012         | L10          | L12  | 0.0673                 |

| K1112         | L11          | L12  | 0.1711                 |

| C1112a        | N11C         | N12C | 1.751e-14              |

| C1112b        | N110         |      | 2.139e-14              |

| K1113         | L11          | L13  | 0.0558                 |

| K1213         | L12          | L13  | 0.1097                 |

| C1213a        | N12C         | N13C |                        |

| C1213b        | N120         | N130 | 5.863e-15              |

| К1214         |              | L14  |                        |

| K1314         | L13          | L14  | 0.1715                 |

| C1314a        | N13C         | N14C |                        |

| C1314b        | N130         | N140 |                        |

| К1315         | L13          | L15  | 0.0678                 |

| K1415         | L14          | L15  | 0.1573                 |

| C1415a        | N14C         | N15C | 1.636e-14              |

| C1415b        | N140         | N150 |                        |

| K1416         | L14          | L16  | 0.0682                 |

| K1516         | L15          | L16  | 0.1707                 |

| C1516a        | N15C         | N16C | 1.748e-14              |

| C1516b        | N150         | N160 |                        |

| .ENDS PACKAGE |              |      |                        |

| *             |              |      |                        |

\* \*

GigaComm is a trademark of Semiconductor Components Industries, LLC (SCILLC).<sup>4</sup> Adobe, Acrobat, and Reader are registered trademarks of Adobe Systems Incorporated.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use personal states CILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.